PROFINET

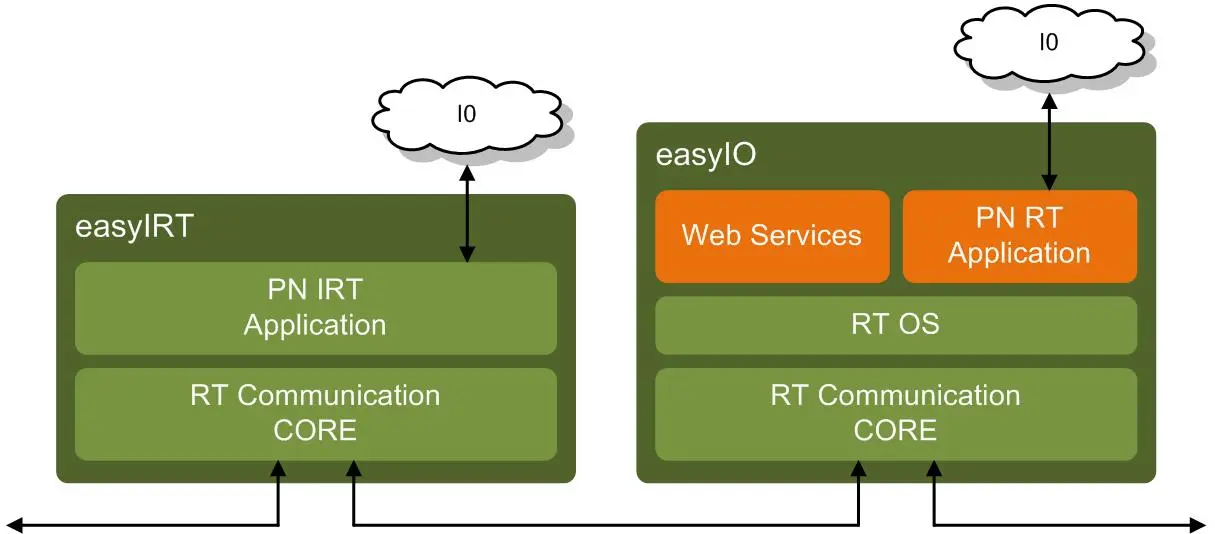

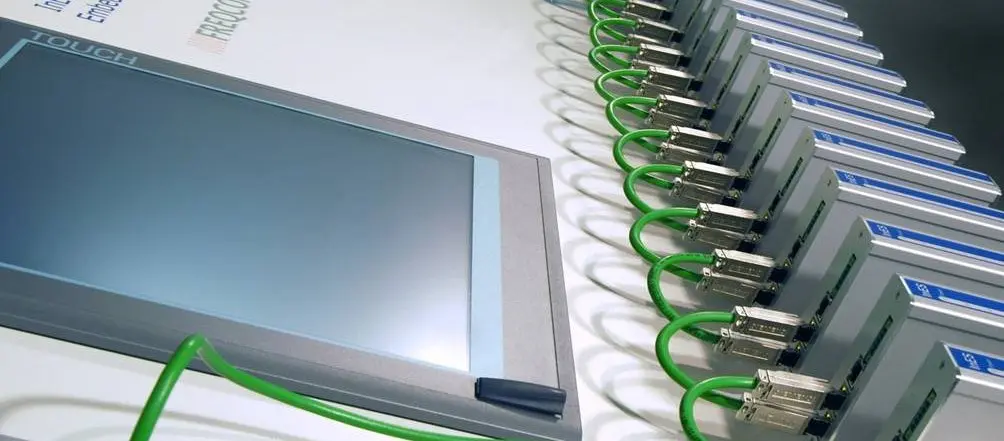

InES pioneered the optimisation of communication stack performance through use of appropriate hardware. The PROFINET ecosystem is well served by suitable and high-performance software stacks. To tickle the maximum performance from this software appropriate hardware architectures are required. InES, on the basis of a universal Real-Time Ethernet controller platform, offers easyIO and easyIRT, two hardware platforms for optimal implementation of PROFINET nodes. Both solutions are low-footprint, highly configurable PROFINET device solution designed specifically for high-performance distributed automation systems.

Key Features:

- Compatible with Profinet 2.3 Conformance Class C

- IRT cycle times as low as 31.25 µs (optional)

- Support for dynamic frame packing (optional)

- Integrated IEEE 1588 PTP implementation

- Integrated 3-port Real-Time Ethernet switch

- Support for non-real-time traffic

- Linux driver available

- AXI Streaming interfaces for real-time data (optional)

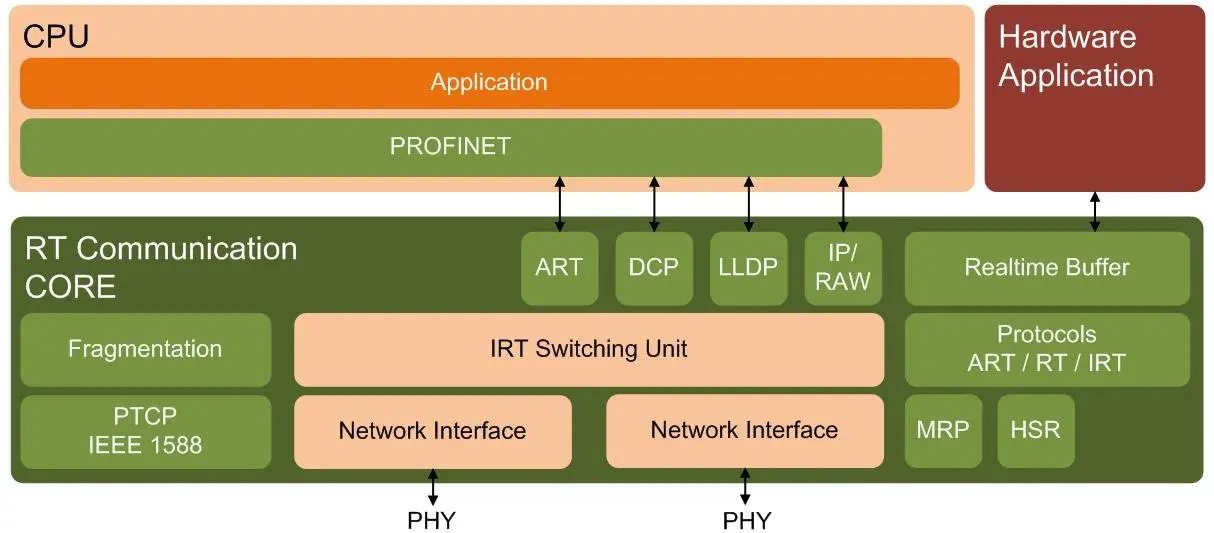

Both products separate buffers for different frame/protocol types, optimising microcontroller resources in accessing received Frames.

The IP cores are optimised for use in FPGA but can be adapted and licensed for use in ASIC.

easyIO

easyIO presumes the use of a soft-core microcontroller running an operating system. InES has experience with eCOS, Linux, VxWorks, NetOS and other popular operating systems.

As shown, easyIO provides separate buffers for LLDP and DCP frames, used in the boot-process, IP legacy traffic as well as ART and RTA frames.

The Siemens PROFINET stack has been ported to this platform and could be successfully demonstrated, compatible to all other devices, at the first PROFINET IO devices PlugFest, March 2009. Other stacks may be easily ported to this platform, full documentation is provided.

<svg xmlns="http://www.w3.org/2000/svg" viewbox="0 0 256 256" class="iconpack phosphor phosphor-arrow-up-right-bold" fill="currentColor" role="img"><rect width="256" height="256" fill="none"></rect><line x1="64" y1="192" x2="192" y2="64" fill="none" stroke="currentColor" stroke-linecap="round" stroke-linejoin="round" stroke-width="24"></line><polyline points="88 64 192 64 192 168" fill="none" stroke="currentColor" stroke-linecap="round" stroke-linejoin="round" stroke-width="24"></polyline></svg>easyIRT / easyIORT Communication Core(PDF 137,3 KB)

easyIRT

easyIRT unleashes the full power of the RT Communication Core.

Overview

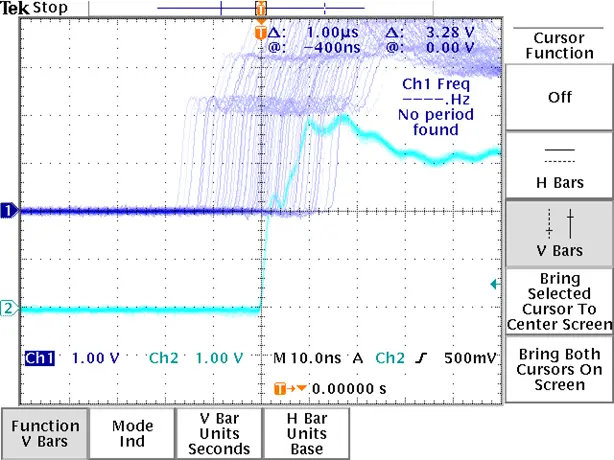

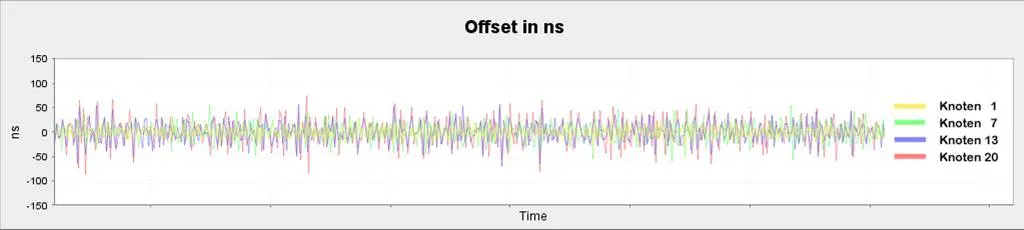

The Profinet IRT IP core, developed by InES, can easily be combined with other IP cores to build entire System on Chip (SoC) solutions. Featuring a complete IEEE 1588 PTP implementation in hardware, this core can uphold standard cycle times of 31.25us without batting the proverbial eye. Using a 400MHz timestamp synchronisation accuracy of 60ns over 20 nodes can be reached.

Isochronous traffic can completely bypass the software stack and directly, or through appropriate VHDL-coded conditioning circuitry, read or write I/O.

easyIRT also provides top-performance optimisations such as preamble shortening and dynamic frame hacking and packing optimising the time-on-the wire for small payload frames. For smaller cycle times, automatic IP frame fragmentation and reassembly is provided.

PTP 4 PROFINET

The ability of PROFINET to ensure bandwidth efficiency is due to clock distribution and synchronisation as provided by IEEE 1588 PTP. IEEE 1588 represents a discrete digital control algorithm acting on a continuous analog transfer function acting on the system quartz. The rate of change of synchronisation between two nodes is directly dependent on the rate of change of the slave clock, more precisely the relative change of the master and slave clock, which is also directly dependent to the rate of change of external influences (acceleration, temperature, pressure) on the system quartz. For high precision synchronisation, effectively a small error rate, the sampling time must be much smaller than this rate. The sampling time however is dependent on the cycle time of the communication system. An optimal cycle time of 1ms can only be upheld in a communication cycle time of 2 ms by multiple transmission of SYNC frames within that cycle. For many implementations a standard software implementation of IEEE 1588 is sufficient.

In high performance systems with low cycle times (>125ns) it can be recommendable to send a SYNC frame every cycle-time. The issue here is that with especially fast cycle times the system processor may be absorbed with servicing the PTP algorithm - in order to service the application a higher-power processor may be needed thus increasing system cost.

A perfect remedy to this situation is to implement the PTP algorithm in “portable hardware”, specifically VHDL code. The incoming SYNC frames and the resultant DELAY REQ/RES frames may be automatically processed and the system clock synchronised without any processing required from the system processor.

The InES easyPTP solution is a 100% portable VHDL solution for implementing a PTP stack in either an ASIC or in a FPGA.

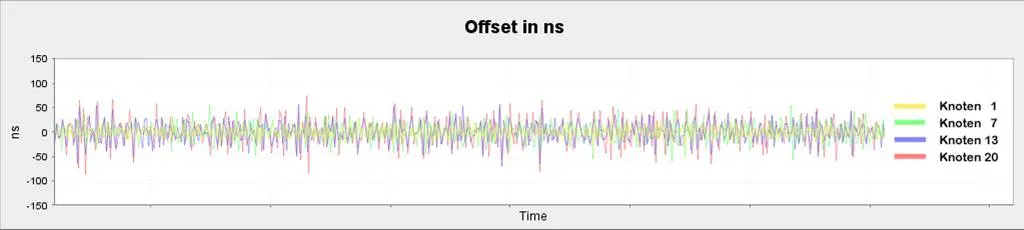

The precision of synchronisation is also (dramatically) dependent on the sampling clock of the time-stamps inserted into the SYNC and DELAY frames. With a standard sampling frequency of 50MHz, a typical FPGA internal clocking rate, a synchronisation precision over 4 nodes of 50ns is easily achieved.

Using a sampling frequency of 400MHz a precision of ca. 60ns may be achieved over 20 nodes.

Contact us for further information concerning optimal node synchronisation in PROFINET or Industrial Ethernet applications.

Competence Center

Training, Consulting, Solutions

InES has been a PROFINET International Competence Center and a regular contributor to the PICC conferences and exhibitor at fairs since 2003. InES, with its partners, offers trainings, consulting and technical support for PROFINET developers and manufacturers.